# Development of Improved Diode Clamped Multilevel Inverter Using Optimized Selective Harmonic Elimination Technique

Tariq Kamal, Syed Zulqadar Hassan, Syeda Zahra Naqvi, Imranullah

Department of Electronics Engineering University of Engineering & Technology Peshawar, Abbottabad Campus, Pakistan

### ABSTRACT

In this paper the role of Selective Harmonic Elimination (SHE) is presented for diode clamped twelve-level multilevel inverter (DCMLI) based on dog leg optimization algorithm. Non-linear equations has been solved to eliminate specific low order harmonics, using the developed DOP algorithm, while at the same time the fundamental component is retained efficiently. The non-linear nature of transcendental equation provide multiple or even no solution for a particular modulation index. The proposed optimization method solving the nonlinear transcendental equations providing all possible solutions. The paper also showing the comparison between different modulation techniques including the proposed method. The entire system has been simulated using MATLAB/Simulink. Simulation results confirm the effectiveness with negligible THD.

## **KEYWORDS**

DCMLI,SHEPWM, Switching Angles, DOP, THD

# I. INTRODUTION

In power electronics, the development of multilevel inverter provide a new and alternative option in high power applications. The high voltage sharing ability, low electromagnetic interference (EMI), lower harmonics, made multilevel inverter a very hot area in today's power system and large motor drives. It is not difficult to develop high voltage inverters with multilevel structure in which voltage are controlled, but the main problem is the harmonic distortion in the output waveform. Recently many modulation techniques such as SPWM, SVPWM, SHEPWM, etc<sup>[1]</sup> have been used to address this problem. SHEPWM technique can lower the harmonic content of the output current as well as resonant harmonic. In the same manner different types of multilevel are used for the purpose of reduction in harmonics and improvement in power quality<sup>[2]</sup>. Cascaded five level multilevel inverter using DSTATCOM implemented for power improvement<sup>[3]</sup>.Chopper with flying capacitor used in DCMLI for the reduction of stress and produces AC voltage<sup>[4]</sup>. The paper<sup>[5]</sup> presents voltage sharing for high power factor loads based on DCMLI(4-levels). SVPWM based<sup>[6]</sup> 3-level diode clamped multilevel level inverter is presented for leakage current in PV system. 3-level DCMLI with ANPC, ZCT used for sustainable energy<sup>[7]</sup>.Building H-Bridge for AC to DC conversion with the use of capacitors and

single DC source with less harmonics<sup>[8]</sup>. Using different voltage balancing equations and techniques to form a flying capacitor H-Bridge multilevel inverter<sup>[9]</sup>.Cascaded inverters with particle swarm optimization technique to improve power quality and reduce total harmonics<sup>[10]</sup>.Cascaded inverter using SVPWM to minimize harmonics and switching frequency<sup>[11]</sup>.Many multi -level inverters are used but diode clamped multi-level inverter (DCMLI) is employed for many applications like power drives & utility system<sup>[12]</sup>.

In this proposed method diode clamped 12 level inverter is implemented using selective harmonic elimination pulse width modulation technique (SHEPWM) to reduce the total harmonic distortion of the output wave form and improve quality of power. Optimization technique dog leg is used for switching angles of IGBTs employed in the system and the switching angles are solved by non-linear transcendental equations which contain trigonometric terms. Newton-Repshan is used to solve these transcendental equations.

### **II. WORKING PRINCIPLE**

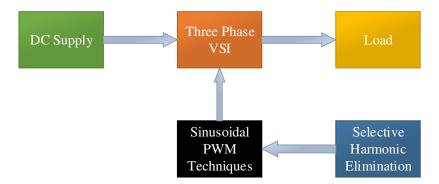

The basic working principle block diagram of SHE was shown in Figure 1. Table 1 shows the number of on and off switches for different levels of output voltage in a half cycle  $(0to90^\circ)$  for 12 levels DCMLI's. At any level number of on switches = (m/2)-1 while each switch is turned on once at a time.

Figure 1 Block Diagram of Selective Harmonic Elimination

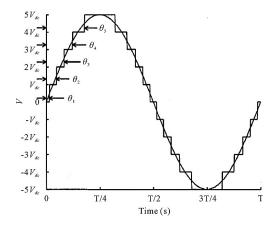

The output of DCMLI is a stepped waveforms shown in Figure 2 for each step IGBT is switched at an angle such that the total harmonic distortion is reduced. To get a desired value of fundamental component of voltage and reduced THD, Selective harmonic elimination PWM method is used. Selective Harmonic elimination (SHEPWM) is used for low switching frequency and removing lower order odd harmonics such as  $3^{rd}$ , 5th,  $7^{th}$ ,  $11^{th}$  and  $13^{th}$ . This method further uses of iterative optimization technique 'trust region dogleg' algorithms to compute switching angles ( $\alpha$ ).

| Stepped Voltages | Conducting Switches                           | Non Conducting Switches                |

|------------------|-----------------------------------------------|----------------------------------------|

| 0Vdc             | 12 13 14 15 16 17 18 19 20 21 22 23 24 25     | 1 2 3 4 5 6 7 8 9 10 11 34 35 36 37 38 |

|                  | 26 27 28 29 30 31 32 33                       | 39 40 41 42 43 44                      |

| 1Vdc             | 11 12 13 14 15 16 17 18 19 20 21 22 23 24     | 1 2 3 4 5 6 7 8 9 10 33 34 35 36 37 38 |

|                  | 25 26 27 28 29 30 31 32                       | 39 40 41 42 43 44                      |

| •                | •                                             | •                                      |

| •                | •                                             | •                                      |

| •                | •                                             | •                                      |

| 10Vdc            | 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 | 1 24 25 26 27 28 29 30 31 32 33 34 35  |

|                  | 20 21 22 23                                   | 36 37 38 39 40 41 42 43 44             |

| 11Vdc            | 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18  | 23 24 25 26 27 28 29 30 31 32 33 34 35 |

|                  | 19 20 21 22                                   | 36 37 38 39 40 41 42 43 44             |

Table 1IGBTs Switching Pattern for 12 DCMLI

Figure 2: Stepped Diode Clamped Multi Level Inverter Output

#### **III. CALCULATION FOR DOG LEG ALGORITHM**

Equations of the output voltage of DCMLI, peak values of harmonics for the calculation of THD and the system of non- linear equations for switching angles calculation are derived from Fourier series. Fourier series for a periodic function is expressed in (1)

$$f_{t} = a_{v} + \sum_{n=1}^{\infty} a_{n} \cos(2\pi n f_{o} t) + b_{n} \sin(2\pi n f_{o} t)$$

(1)

Here  $a_v$ ,  $a_n$  and  $b_n$  are the Fourier series coefficients and  $f_o$  is the fundamental frequency. (2), (3) & (4) shows relationships to determine the values of these coefficients

$$a_{v} = \frac{1}{T} \int_{t_{o}}^{t_{o}+T} f(t) dt$$

(2)

$$a_{n} = \frac{2}{T} \int_{t_{o}}^{t_{o}+T} f(t) \cos(2\pi n f_{o} t) dt$$

(3)

$$b_n = \frac{2}{T} \int_{t_o}^{t_o+T} f(t) \sin(2\pi n f_o t) dt$$

(4)

Where  $t_o$  = Chosen time reference, T = Fundamental period.

For a signal having odd quarter wave Symmetry, Fourier series coefficients are given as

$$a_{v} = 0$$

$a_{n} = 0$  for all  $n$   $b_{n} = 0$  for  $n$  even

And

$$b_n = \frac{8}{T} \int_0^{T/4} f(t) \sin(2\pi n f_o t) dt \qquad for \ odd \ n$$

(5)

The Multilevel inverter has odd quarter wave symmetry. Using Fourier coefficient equations of a quarter waves, Fourier coefficients for a DCMLI output are derived in terms of switching angles. Five angles are considered here only for mathematical calculations.

$$b_{n} = \frac{4}{\pi} \int_{0}^{\frac{\pi}{2}} f(\frac{\omega t}{2\pi f_{o}}) \sin(n\omega t) d(\omega t) \quad \text{for } n \text{ odd}$$

$$b_{n} = \int_{\alpha_{1}}^{\alpha_{2}} \frac{4}{\pi} (v_{dc}) \sin(n\omega t) d(\omega t) + \int_{\alpha_{2}}^{\alpha_{3}} \frac{4}{\pi} (2v_{dc}) \sin(n\omega t) d(\omega t) + \int_{\alpha_{3}}^{\alpha_{4}} \frac{4}{\pi} (3v_{dc}) \sin(n\omega t) d(\omega t) + \int_{\alpha_{4}}^{\alpha_{5}} \frac{4}{\pi} (4v_{dc}) \sin(n\omega t) d(\omega t) + \int_{\alpha_{5}}^{\alpha_{5}} \frac{4}{\pi} (5v_{dc}) \sin(n\omega t) d(\omega t)$$

$$(6)$$

$$+ \int_{\alpha_{5}}^{\frac{\pi}{2}} \frac{4}{\pi} (5v_{dc}) \sin(n\omega t) d(\omega t)$$

$$(7)$$

where  $\alpha_1, \alpha_2, \alpha_3, \alpha_4$  and  $\alpha_5$  are the switching angles

Solving Integration results

$$b_{n} = \frac{4}{\pi} \int_{0}^{\frac{\pi}{2}} f\left(\frac{\omega t}{2\pi f_{o}}\right) \sin(n\omega t) d(\omega t) \quad \text{for } n \text{ odd}$$

$$b_{n} = -\frac{4}{\pi n} v_{dc} \left[\cos(n\omega t)\right]_{\alpha_{1}}^{\alpha_{2}} - \frac{4}{\pi n} (2v_{dc}) \left[\cos(n\omega t)\right]_{\alpha_{2}}^{\alpha_{3}}$$

$$-\frac{4}{\pi n} (3v_{dc}) \left[\cos(n\omega t)\right]_{\alpha_{3}}^{\alpha_{4}} - \frac{4}{\pi n} (4v_{dc}) \left[\cos(n\omega t)\right]_{\alpha_{4}}^{\alpha_{5}}$$

$$-\frac{4}{\pi n} (5v_{dc}) \left[\cos(n\omega t)\right]_{\alpha_{1}}^{\alpha_{2}} - \frac{4}{\pi n} (2v_{dc}) \left[\cos(n\omega t)\right]_{\alpha_{5}}^{\alpha_{5}} \tag{8}$$

20

$$= \frac{4}{\pi n} v_{dc} [\cos(n\alpha_1) - \cos(n\alpha_2)] + \frac{4}{\pi n} (2v_{dc}) [\cos(n\alpha_2) - \cos(n\alpha_3)] + \frac{4}{\pi n} (3v_{dc}) [\cos(n\alpha_3) - \cos(n\alpha_4)] + \frac{4}{\pi n} (3v_{dc}) [\cos(n\alpha_4) - \cos(n\alpha_5)]$$

(9)

Where n is an odd integer

$$\cos\left(n\frac{\pi}{2}\right) = 0 , \ b_n = \frac{4}{\pi n} v_{dc} \left[\cos(n\alpha_1) + \cos(n\alpha_2) + \cos(n\alpha_3) + \cos(n\alpha_4) + \cos(n\alpha_5)\right]$$

(10)

(10)provides peak values of odd harmonics in a DCMLI which can be used to calculate total harmonic distortion (THD) using(11).

$$THD = \frac{\sqrt{v_2^2 + v_3^2 + v_4^2 \dots v_n^2}}{v_1} v_1, v_2, v_3, \dots, v_n \text{ are the peak values of harmonics}$$

(11)

Using resultant theory, a set of non-linear equations is derived from(10)which can is solved for the values of angles. In case of twenty fourlevelsDCMLI, following set of equations is obtained to eliminate odd harmonics up to eleventh level.

$$\cos(3\alpha_1) + \cos(3\alpha_2) + \cos(3\alpha_3) + \dots + \cos(3\alpha_{11}) = 0 \tag{12}$$

$$\cos(7\alpha_1) + \cos(7\alpha_2) + \cos(7\alpha_3) + \dots \cos(7\alpha_{11}) = 0$$

(13)

$$\cos(9\alpha_1) + \cos(9\alpha_2) + \cos(9\alpha_3) + \dots \cos(\alpha_{11}) = 0 \tag{14}$$

$$\cos(11\alpha_1) + \cos(11\alpha_2) + \cos(11\alpha_3) \dots + \cos(11\alpha_{11}) = 0$$

(15)

$$\cos(\alpha_1) + \cos(\alpha_2) + \cos(\alpha_3) + \dots \cos(\alpha_{11}) = \frac{mM\pi}{4}$$

(16)

$$M = \frac{v_1}{v} \tag{17}$$

m = (number of levels/2)-1

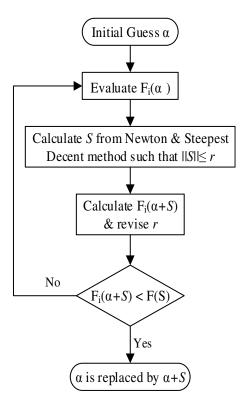

Switching angles are calculated with the help of MATLAB program using trust region dogleg algorithm (shown in fig) for a range of modulation indexes. Table 2 angles are calculated using (18) is satisfied.

$$(0 \le \alpha_1 \le \alpha_2 \le \alpha_3 \le \alpha_4 \le \alpha_5 \le \alpha_6 \le \alpha_7 \le \alpha_8 \le \alpha_9 \le \alpha_{10} \le \alpha_{11})$$

(18)

Where  $\alpha$  is an array containing initial guess for  $\alpha_1 + \alpha_2 + \dots + \alpha_n$

Figure 3: Proposed Dog Leg Algorithm

$$F(\alpha) = \sum_{i=1}^{n} \left[ F_i(\alpha) \right]^2$$

(19)

S is correction step and r is radius of trust region. Figure 4 shows the proposed flow chart of trust region dogleg method for computing  $\alpha_1 + \alpha_2 + \dots + \alpha_n$  from set of functions  $f_1, f_2, f_3, \dots, f_n$

In first step, a correction step is calculated which is added to the initial guess. Dogleg utilizes Newton and steepest descent methods. The combination of these two methods ensures a fast convergence and a solution of function in the steepest descent direction. The second step involves finding the value of trust region radius to estimate length of step for the current iteration such that the following condition is obeyed.

$$F(\alpha + s) < F(\alpha) \tag{20}$$

Third step performs a check the new values of function. Has the function minimized.

| М   | $\alpha_{1}$ | $\alpha_{2}$ | $\alpha_{3}$ | $lpha_{_4}$ | $\alpha_{_5}$ | $\alpha_{_6}$ | $\alpha_{_7}$ | $\alpha_{_8}$ | $\alpha_{_{9}}$ | $lpha_{10}$ | $\alpha_{_{11}}$ |

|-----|--------------|--------------|--------------|-------------|---------------|---------------|---------------|---------------|-----------------|-------------|------------------|

| 0.9 | 0.054        | 0.146        | 0.246        | 0.333       | 0.435         | 0.574         | 0.675         | 0.771         | 0.982           | 1.119       | 1.500            |

| 5   | 1            | 3            | 1            | 1           | 6             | 0             | 7             | 3             | 4               | 5           | 9                |

| 0.9 | 0.000        | 0.150        | 0.240        | 0.359       | 0.491         | 0.603         | 0.710         | 0.838         | 1.030           | 1.325       | 1.530            |

|     | 0            | 2            | 8            | 3           | 6             | 6             | 6             | 0             | 4               | 3           | 8                |

| 0.8 | 0.000        | 0.173        | 0.262        | 0.400       | 0.493         | 0.613         | 0.805         | 0.895         | 1.165           | 1.418       | 1.660            |

| 5   | 0            | 1            | 3            | 3           | 4             | 7             | 6             | 8             | 9               | 8           | 4                |

| 0.8 | 0.000        | 0.169        | 0.315        | 0.390       | 0.530         | 0.689         | 0.821         | 1.023         | 1.291           | 1.487       | 1.570            |

|     | 0            | 4            | 5            | 6           | 8             | 6             | 2             | 7             | 6               | 0           | 8                |

| 0.7 | 0.000        | 0.187        | 0.328        | 0.419       | 0.576         | 0.742         | 0.892         | 1.156         | 1.407           | 1.542       | 1.57             |

| 5   | 0            | 0            | 7            | 6           | 1             | 8             | 9             | 8             | 8               | 4           |                  |

| 0.7 | 0.000        | 0.249        | 0.282        | 0.483       | 0.632         | 0.777         | 0.029         | 1.229         | 1.464           | 1.561       | 1.570            |

|     | 0            | 9            | 6            | 4           | 2             | 9             | 6             | 0             | 5               | 7           | 0                |

Table 2: Optimized switching angles in radians for 12 level DCMLI

# **IV. IMPLEMENTATION OF 12 LEVEL DCMLI USING SHEPWM**

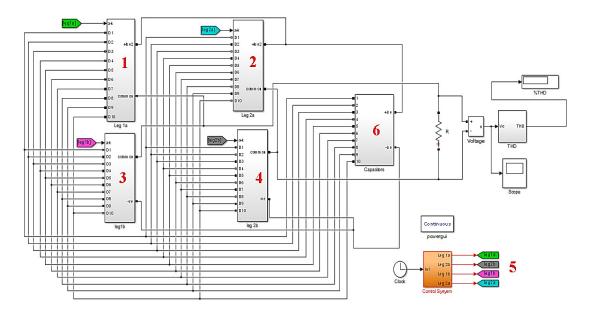

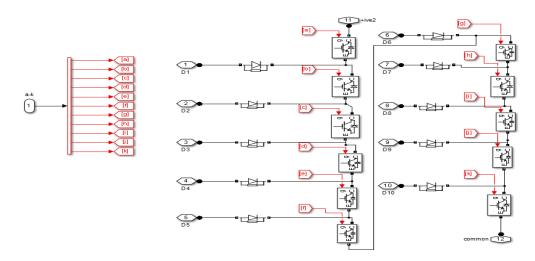

12 level diode clamped multilevel inverter (DCMLI) with four sub-systems connected to DC batteries sources and switches state controller (SSC) is shown in fig.01.it consists of specific number of diodes, switches (IGBT's) and DC sources. The components required are calculated using equations 1, 2, 3.

Number of IGBTs = 4[(m/2)-1] (21)

Number of IGBTs =44

Number of clamping diodes=

$$\{(m/2)-1\}$$

\* $\{(m/2)-2\}$  (22)

| Number of clamping diodes =110     |      |

|------------------------------------|------|

| Number of batteries= $(m / 2) - 1$ | (23) |

Number of batteries =11

Emerging Trends in Electrical, Electronics & Instrumentation Engineering: An international Journal (EEIEJ), Vol. 1, No. 3, August 2014

Figure 4: 12 Levels DCMLI

Figure 4 shows the overall system of DCMLI. In figure,1 & 3 shows the first leg of positive terminal of output DC similarly 2 & 4 shows the 2<sup>nd</sup> leg of negative terminal of output DC. 5 generates the control signals to legs and 6 contains the number of capacitors for multilevel arrangement. Figure 5 shows Leg 1a of 12 levels DCMLI which is connected in series with leg1b to complete first leg as there are two legs in this system. Second leg is similar to first leg. Both first and second legs are connected to form a full H-Bridge DCMLI.

## **V. SIMULATION RESULTS**

Experimental results are obtained for optimized switching angles using dog leg method and for non-optimized IGBTs switching angles. Experimental results include shows

- Values of total harmonic distortion

- Harmonic order of harmonics with reference to fundamental component

- Effect of modulation index on THD.

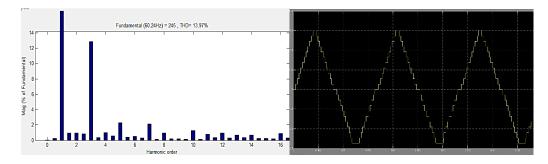

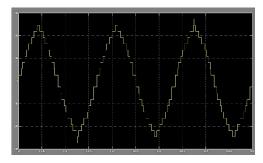

Figure 6: THD and Frequency spectrum of 12 Level DCMLI non- optimized and m=0.95

Figure 7: Voltage Waveform of 12 levels DCMLI with non-optimized angles

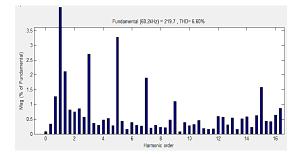

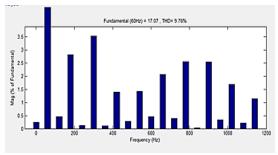

Figure 8: THD and Frequency spectrum of 12level DCMLI with optimized angles

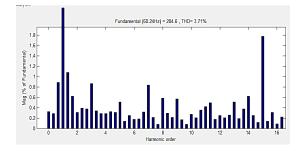

Figure 10: THD and Frequency spectrum of 12 level DCMLI DCMLI with optimized angles (m=0.95)

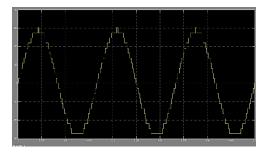

Figure 9: Voltage Waveform of 12 Level DCMLI levels optimized and m =0.7

Figure 11:Voltage Waveform of 12 Level optimized and m =0.95

Emerging Trends in Electronics & Instrumentation Engineering: An international Journal (EEIEJ), Vol. 1, No. 3, August 2014

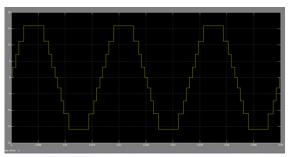

Figure 12: THD and Frequency spectrum of Figure 13:Voltage Waveform of 5- Level DCMLI 5-levels DCMLI with optimized angles (m=0.95) optimized and m=0.95

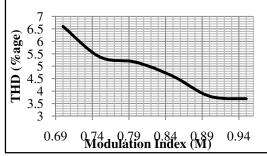

Table 3 shows the THD at different modulation indexes and Figure 14 show that the THD will decrease as modulation index increases.

| М    | THD  |

|------|------|

| 0.95 | 3.80 |

| 0.9  | 4.80 |

| 0.85 | 5.65 |

| 0.8  | 5.80 |

| 0.75 | 6.12 |

| 0.7  | 6.49 |

Table 3:THD at different Modulation index

Figure 14:Comparison of THD vs Modulation Index

Table 4 shows a comparison of various techniques employed for 5-level diode clamped inverter to reduce total harmonic distortion(THD).modulation techniques like POD-PWM, SPWM, Third harmonic injection, offset voltage and trapezoidal are used but proposed technique in this paper improves output voltage waveform with lowest THD value and power factor value near to 1.

| No. | Modulation Technique                           | %THD  |

|-----|------------------------------------------------|-------|

| 1   | POD-PWM <sup>[12]</sup>                        | 32.32 |

| 2   | Trapezoidal <sup>[13]</sup>                    | 18.39 |

| 3   | Three harmonic Injection <sup>[14]</sup>       | 17.57 |

| 4   | Third harmonic injection <sup>[13]</sup>       | 17.03 |

| 5   | SPWM <sup>[13]</sup>                           | 16.97 |

| 6   | SPWM <sup>[15]</sup>                           | 16.82 |

| 7   | Offset voltage <sup>[13]</sup>                 | 16.38 |

| 8   | Proposed Technique (SHEPWM)With Dog Leg Method | 9.76  |

Table 4: THD values of 5-level multilevel diode clamped inverters using different modulations techniques

#### **VI. CONCLUSION**

In this paper, SHEPWM strategy is taken under consideration for elimination of desired low order harmonics. The corresponding switches angles for DCMLI is calculated using dog leg

optimization algorithm. Undesired harmonics are eliminated to possible maximum limits and the fundamental voltage is maintained at desired level, thus resulting the minimum THD. The proposed technique can be applied to any multilevel inverter configurations and we can generalize this method to any higher order inverters.

### REFERENCES

- [1] Peddapeli.S.K, (2014) "Recent Advances in Pulse Width Modulation Techniques and Multilevel Inverters" International Journal of Electrical, Electronic Science and EngineeringVol 8 No 3, pp-568-576.

- [2] Hussein. H, (2014) "Harmonics Elimination PWM (HEPWM)" International Journal of Engineering Research and General Science Vol 2, No 2, pp-172-181.

- [3] Satyanarayana, G. V. R., & Ganesh, S. N. V, (April 2010)"Cascaded 5-level inverter typeDSTATCOM for power quality improvement"InStudents' Technology Symposium (TechSym), 2010 IEEE (pp. 166-170).

- [4] Shukla, A., Ghosh, A., & Joshi, A, (2010) "Flying-capacitor-based chopper circuit for dc capacitor voltage balancing in diode-clamped multilevel inverter" Industrial Electronics, IEEE Transactions on, 57(7), pp2249-2261.

- [5] Boora, A. A., Nami, A., Zare, F., Ghosh, A., &Blaabjerg, F, (2010) "Voltage-sharing converter to supply single-phase asymmetrical four-level diode-clamped inverter with high power factor loads"Power Electronics, IEEE Transactions on, 25(10), pp2507-2520.

- [6] Cavalcanti, M. C., Farias, A. M., Oliveira, K. C., Neves, F. A., &Afonso, J. L, (2012)"Eliminating leakage currents in neutral point clamped inverters for photovoltaic systems" Industrial Electronics, IEEE Transactions on, 59(1), pp435-443.

- [7] Li, J., Liu, J., Boroyevich, D., Mattavelli, P., &Xue, Y, (May, 2011) "Comparative analysis of three-level diode neural-point-clamped and active neural-point-clamped zero-current-transition inverters" In Power Electronics and ECCE Asia (ICPE & ECCE), 2011 IEEE 8th International Conference (pp. 2290-2295)

- [8] Du, Z., Tolbert, L. M., Ozpineci, B., & Chiasson, J. N, (2009) "Fundamental frequency switching strategies of a seven-level hybrid cascaded H-bridge multilevel inverter" Power Electronics, IEEE Transactions on, 24(1), pp25-33.

- [9] Khazraei, M., Sepahvand, H., Corzine, K. A., &Ferdowsi, M, (2012) "Active capacitor voltage balancing in single-phase flying-capacitor multilevel power converters". Industrial Electronics, IEEE Transactions on, 59(2), pp769-778.

- [10] Rodriguez, J. C., & P Moran, L, (2001) "A vector control technique for medium voltage multilevel inverters" Applied Power Electronics Conference and Exposition, 2001.APEC 2001.

- [11] J. Rodriguez, J. S. Lai, and F. Z. Peng, (2002) "Multilevel inverters: A survey of topologies, controls, and applications" IEEE Trans. Ind. Electron., Vol.49, no. 4, pp. 724–738.

- [12] Chaturvedi. R,(2014) "A Single Phase Diode Clamped Multilevel Inverter and its Switching Function". Journal of Innovative trends in Science, Pharmacy & Technology. Vol-1(1),pp.63-66.

- [13] Haskar Reddy, V. N.,Babu, C. S. & Suresh, K, (2011) "Advanced Modulating Techniques for Diode Clamped Multilevel Inverter Fed Induction Motor" Vol. 6, No 1,pp. 90-99.

- [14] Zheng, X., Song, L., & Hongying, P, "Study of Five-level diodes-clamped Inverter Modulation Technology Based on Three-harmonic Injection Method" 2nd International Conference on Electronic & Mechanical Engineering and Information Technology 2012.

- [15] Kedareswar.M., (2013) "Reduction of THD in Diode Clamped Multilevel Inverter employing SPWM technique"International Journal of Scientific and Research Publications, Vol 3, No 6, pp.1-4.

#### AUTHORS

**Tariq Kamal**, received his BSc degree in Electronic Engineering from University of Engineering and Technology (UET) Peshawar, Pakistan in 2012.He is currently in Comsats institute of information Technology Abbottabad Campus pursuing his Master degree in Electrical Power and Control Engineering and acting as a Lecturer in University of Engineering and Technology (UET) Abbottabad Campus. His main research is in the area of power system stability, application of adaptive intelligent controls, power electronics and electrical Machine drives.

**Syed Zulqadar Hassan**, has received his B.Sc. (Electronics Engineering) from University of Engineering and Technology, Peshawar in 2012 with securing a Gold Medal and also got award from Governor of KPK. Currently his M.Sc. (Electrical Engineering Power & Control) is likely to be completed from Comsats Institute of Information Technology, Abbottabad Campus and recently also performing the duties of Lecturer in University of Engineering and Technology (UET) Abbottabad Campus. His main research focuses on the

Engineering and Technology (UET) Abbottabad Campus. His main research focuses on the area of Fuzzy Based Controller Design and Power Electronics Control.

**Syeda Zahra Naqvi**, received her B.Sc. (Electronics Engineering) from University of Engineering and Technology, Peshawar in 2013. Currently she is engaged in doing M.Sc. (Electrical Engineering Power & Control) form Comsats Institute of Information Technology, Abbottabad Campus. Her main research is in the area of Power System and Power Electronics Control.

**Imranullah**, received his BSc degree in Electronic Engineering from University of Engineering and Technology (UET) Peshawar, Pakistan in 2012.He is currently in University of Engineering & Technology Taxila pursuing his Master degree in Control Engineering. His main research is in the area of Control stability, Power electronic Control system.